© ROOT-NATION.com - Використання контенту дозволено за наявністю зворотнього посилання.

Сьогодні розкажемо про транзистори майбутнього та розкриємо всі секрети їх створення. Вже сьогодні стає зрозуміло, що попереду на нас чекає період величезних змін у структурі та способі виробництва чипів, яких ринок не бачив дуже давно. Найвидатніші уми світу проводять безсонні ночі, думаючи про те, яку формулу використовувати, щоб змусити окремі атоми танцювати саме так, як їм потрібно, і робити речі, які, здається, порушують закони фізики.

Це буде також період загострення конкуренції між напівпровідниковими гігантами зі США, Кореї та Тайваню. Саме вони намагаються скористатися майбутньою зміною парадигми, щоб відновити, отримати або зміцнити свої позиції технологічних лідерів. Які саме інновації та революції на нас чекають? Спробуємо сьогодні пояснити.

Також читайте: Що таке AMD XDNA? Архітектура, яка запускає ШІ на процесорах Ryzen

Зміна геометрії транзисторів

А точніше, зміняться їхні цілі. Перше нововведення, яке буде (або було!) представлене великою трійкою виробників напівпровідників (TSMC, Intel, Samsung), це так звані транзистори GAAFET. Це перша така серйозна зміна в геометрії транзистора з 2011 року, коли світ побачив транзистори FinFET від Intel. Я не хочу приділяти багато уваги темі транзисторів GAAFET, бо для цього потрібна окрема стаття. Тут ми обговоримо лише концепцію, що лежить в їх основі.

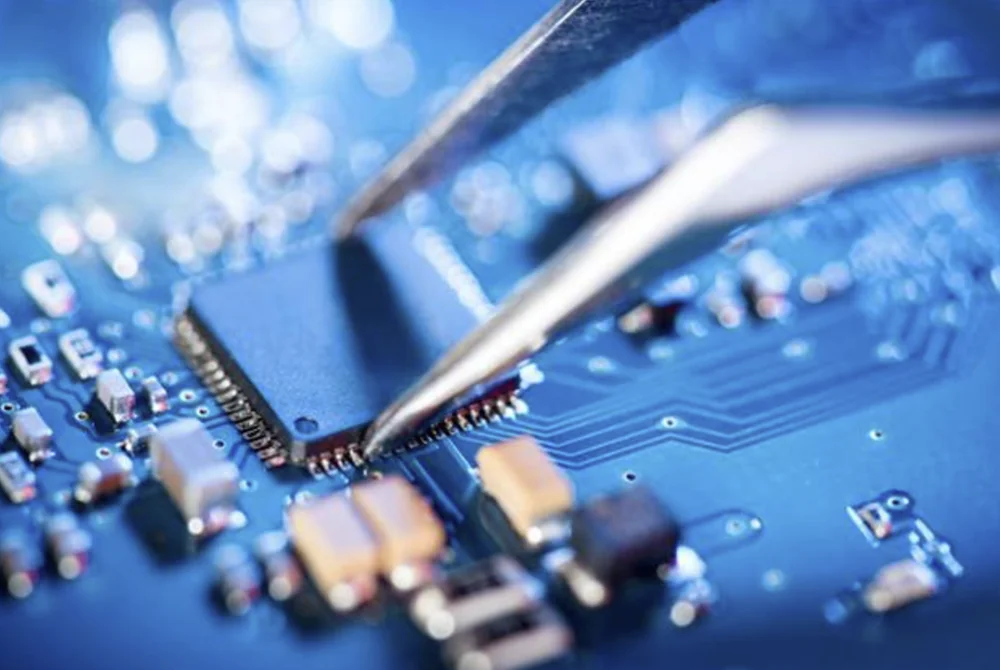

З мініатюризацією транзисторів інженери почали відчувати так звані ефекти короткого каналу. Коротше кажучи, у міру того, як відстань між витоком і стоком транзистора скорочувалася, проблема ставала все більшою і більшою. Тобто, затвор почав втрачати контроль над струмом, що протікає через канал. Протягом дюжини років вирішення цієї проблеми полягало в тому, як зробити так, щоб канал виступав із поверхні кремнієвої пластини як ребро (звідси Fin, або fin, у FinFET). Це дозволяє затвору контактувати з каналом з трьох сторін (або двох, якщо ребро має клиноподібний поперечний переріз), надаючи йому більший контроль над потоком струму та більшу гнучкість в адаптації електричних параметрів транзисторів до потреб дизайну.

Однак постійне зменшення транзисторів означало, що цього вже недостатньо. Необхідно було, щоб затвор почав оточувати транзисторний канал, тобто утворював транзистори GAAFET (GAA – абревіатура від Gate-All-Around). Простіше кажучи, ви можете уявити їх як транзистори FinFET, розміщені з одного боку, оскільки транзистори FinFET часто мають два або три ребра. Це як багаторівневий сендвіч, в якому канали у вигляді труб або листів, розташованих один над одним, розділені шарами ізолятора та затвора. Незважаючи на те, що ця концепція відома протягом багатьох років і використовує існуюче обладнання та процеси, реалізація її не є тривіальною. Проблема полягає в тому, що на якомусь етапі наступні шари каналу висять у повітрі, підтримувані лише тимчасовим “стовпом”. При цьому їх нижня частина повинна бути рівномірно покрита шаром діелектрика товщиною в окремий атом, а потім ретельно заповнювати всі порожні місця з матеріалом.

Той факт, що транзистори GAAFET не є тривіальною справою, підкреслюється ситуацією з Samsung. З 2022 року в портфоліо корейців є процес з транзисторами MBCFET (маркетингова назва Samsung для реалізації транзисторів GAAFET). На практиці, однак, це типова піррова перемога в гонці. Справа в тому, що відсоток повнофункціональних чипів, отриманих з його використанням, настільки низький, що майже ніхто не хоче його використовувати у виробництві (навіть… Samsung для свого Exynos). Все, що ми знаємо, це те, що він застосовується для виробництва невеликих і відносно простих мікросхем для майнерів криптовалюти. Очікується, що тільки друге покоління цього процесу, яке буде доступне в 2024 році, під назвою 3GAP (хоча деякі джерела кажуть, що його можна перейменувати на процес класу 2 нм), буде використовуватися більш широко.

У цьому році транзистори GAAFET (Intel називає свою реалізацію RibbonFET) повинні бути доставлені на заводи Intel в рамках процесів Intel 20A і 18A, які будуть використовуватися для виробництва компонентів систем Arrow Lake і Lunar Lake. Однак різні галузеві чутки свідчать про те, що початкові масштаби виробництва можуть бути обмеженими.

А як справи у TSMC? Тайваньська компанія планує використовувати транзистори GAAFET у своєму процесі N2, який, як очікується, буде повністю готовий лише у 2025 році. Теоретично пізніше, ніж у Samsung і Intel, але коли TSMC говорить про наявність певного процесу, зазвичай це означає готовність виробляти щось для Apple і Nvidia, тому на практиці різниця може бути набагато меншою.

Читайте також: Все про чип Neuralink Telepathy: що це таке і як працює

Зміна способу живлення транзисторів

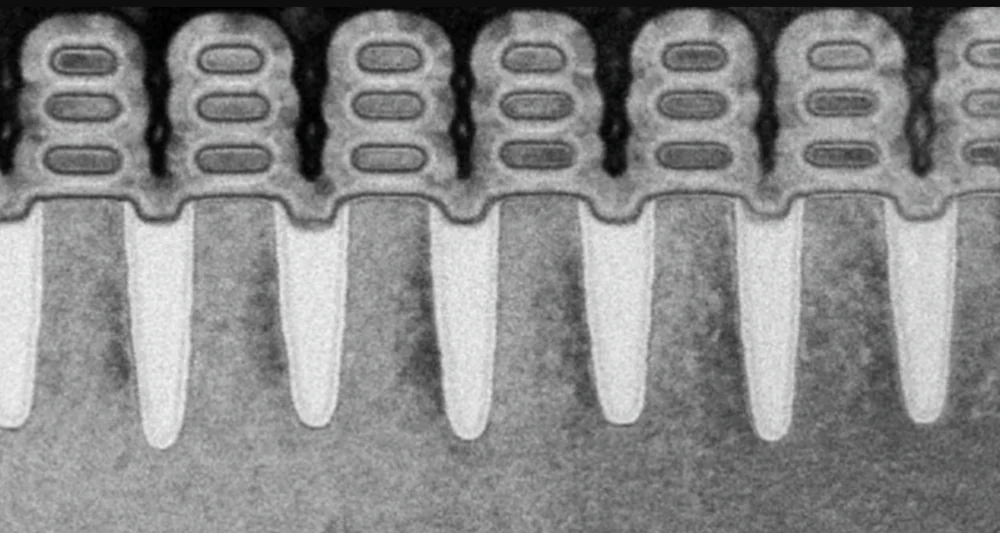

Друга новація, яке на нас чекає, пов’язана з тим, як будуть живитися транзистори в мікросхемах. У даний час процес виробництва мікропроцесора відбувається пошарово знизу вгору. Транзистори будуються внизу, потім над ними будуються з’єднувальні мережі, а потім вже кабелі живлення. Зазвичай існує від десятка до понад двадцяти шарів, і чим вищий шар, тим більші його елементи.

Протягом наступних кількох років стандартом стане те, що після створення з’єднань між транзисторами кремнієва пластина буде перевертатися, тоншати, а шляхи живлення будуть створюватися на іншій, полірованій стороні пластини. Це означає, що транзистори будуть як котлета в бургері, а не як основа торта.

Легко здогадатися, наскільки це ускладнить процес виробництва мікросхем, але, згідно з першими експериментами, процес зворотного живлення BSPDN (Back Side Power Delivery Network) приносить багато переваг. По-перше, завдяки такому підходу транзистори можна розмістити ближче один до одного. По-друге, загальна кількість шарів буде меншою. По-третє, з’єднання від найвищого рівня джерела живлення до транзистора будуть коротшими. А це означає менші втрати енергії та можливість зниження напруги живлення. Точні способи реалізації цього рішення можуть відрізнятися за складністю та потенційними перевагами, але всі основні гравці на ринку кажуть, що гра, безумовно, варта свічок.

Пізніше цього року ми вперше побачимо роботу BSPDN у Intel Process 20A (Intel називає його реалізацію PowerVia). Таким стрімким розвитком подій Intel завдячує тому факту, що вже деякий час працює над цією технологією, незалежно від роботи над зміною геометрії транзисторів і використанням новіших машин. Це означає, що вона зможе інтегрувати її практично в будь-який майбутній процес.

Samsung поки не надала жодної офіційної інформації щодо того, коли вона почне використовувати свою версію процесу зворотного живлення BSPDN. Новин небагато, але ми знаємо, що компанія Intel вже експериментує з цим рішенням. А галузеві чутки говорять про можливість його впровадження в процес SF2, запланований на 2025 рік, або в наступний, який запланований на 2027 рік.

TSMC теж неспішна в цій сфері, і повідомляє, що хоча перші експерименти приносять хороші результати, вона має намір ввести BSPDN в процес N2P, запланований для реалізації тільки на рубежі 2026 і 2027 років.

Читайте також: Телепортація з наукової точки зору та її майбутнє

Зміна машин експонування пластин

Немає серйозної розмови про виробництво мікропроцесорів без згадки про критерій Релея. У випадку літографії, тобто процесу експонування кремнієвих пластин, це набуває вигляду такої формули:

CD = k1 • λ / NA.

Простіше кажучи, це означає, що розмір найменшого елемента, який можна створити світлом на поверхні кремнієвої пластини, залежить від трьох чисел:

k1 – безрозмірний коефіцієнт на практиці, що вказує на ефективність процесу;

λ – довжина хвилі світла, яке освітлює пластину;

NA – числова апертура оптичної системи.

Протягом багатьох років основним способом збільшення щільності упаковки транзисторів було використання світла з дедалі меншою довжиною хвилі. Ми почали з рівня кількох сотень нанометрів і відносно швидко змогли перейти до використання світла з довжиною хвилі 193 нм, на якому світ напівпровідників застряг набагато довше, ніж хотів. Після років досліджень, затримок і витрачених мільярдів доларів у 2019 році машини ультрафіолетової літографії ASML нарешті вийшли на ринок. Вони використовують ультрафіолетове світло (EUV) з довжиною хвилі приблизно 13,5 нм і зараз застосовуються на всіх передових заводах з виробництва мікросхем. Однак це, мабуть, останній раз, коли в наведеній вище формулі вдалося зменшити λ.

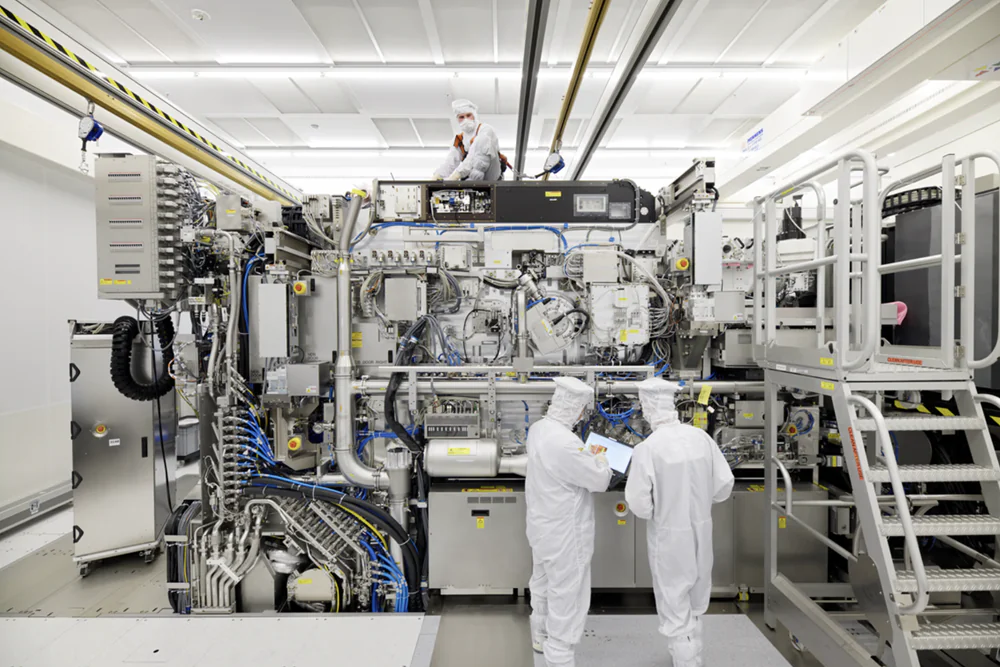

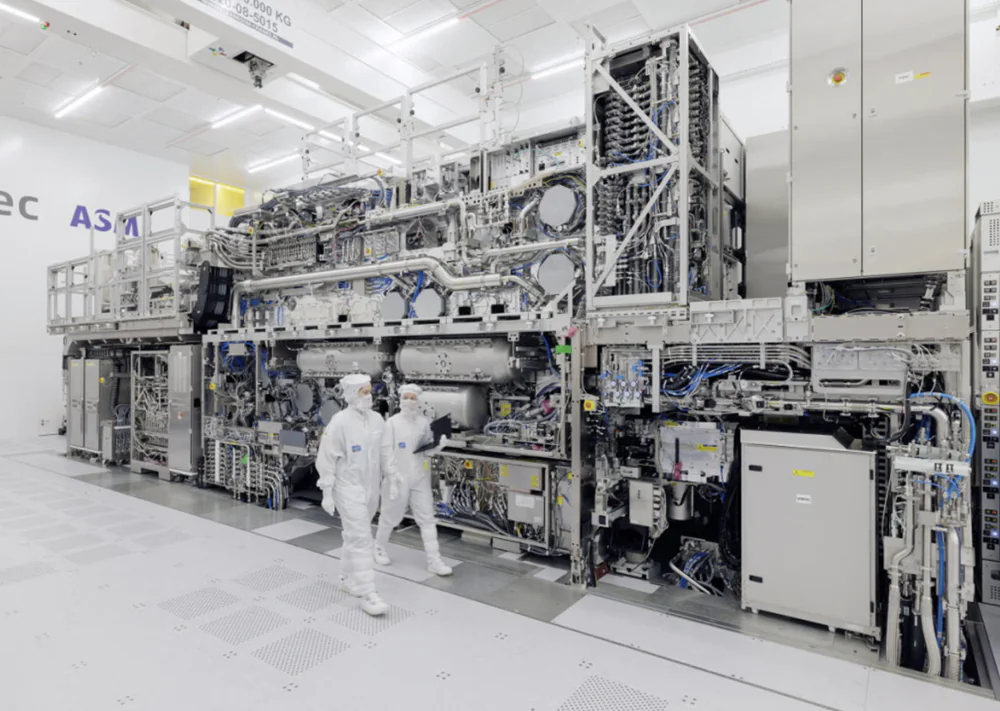

Ось чому доведеться пограти зі зміною NA. Можна розглядати NA як діафрагму об’єктива камери. Це безрозмірне число визначає, скільки світла збирає оптична система. У випадку літографічних машин це означає (згідно з наведеною вище формулою), що якщо ми хочемо створювати все менші й менші елементи, то вищим має бути NA. Машини ASML, які зараз використовуються, мають NA 0,33. Наступний крок — машини з високою числовою апертурою оптичної системи, які мають NA 0,55.

Звучить просто, але в цьому бізнесі немає нічого простого. Про це найкраще свідчить той факт, що машини High-NA набагато більші та більш ніж удвічі дорожчі за своїх попередників (близько $400 млн проти приблизно $150 млн), і водночас мають меншу пропускну здатність. Тому, хоча всі знають, що це майбутнє виробництва найдосконаліших процесорів, це часто сприймається як форма необхідного зла.

Intel найшвидше розпочала використання машин EUV High-NA. Американська компанія вже придбала першу доступну машину такого типу, яка зараз встановлюється на одному з заводів компанії в Орегоні. Також Intel планує купити більшість машин, вироблених цього року. Відомо, що розробники планують використовувати літографію High-NA у великих масштабах в процесі 14A, який, як очікується, побачить світ у 2026 або 2027 році (якщо все піде за планом).

Водночас, Samsung і TSMC не поспішають, сумніваючись в економічному сенсі використання цього обладнання до реалізації 1-нм техпроцесу, тобто приблизно до 2030 року. Натомість вони мають намір вичавити все можливе з EUV-машин, які вони вже мають, за допомогою різних хитрощів і вдосконалень процесу, які підпадають під егіду коефіцієнта k1.

Також цікаво: Як Тайвань, Китай і США борються за технологічне домінування: велика війна чипів

Перехід на 3D

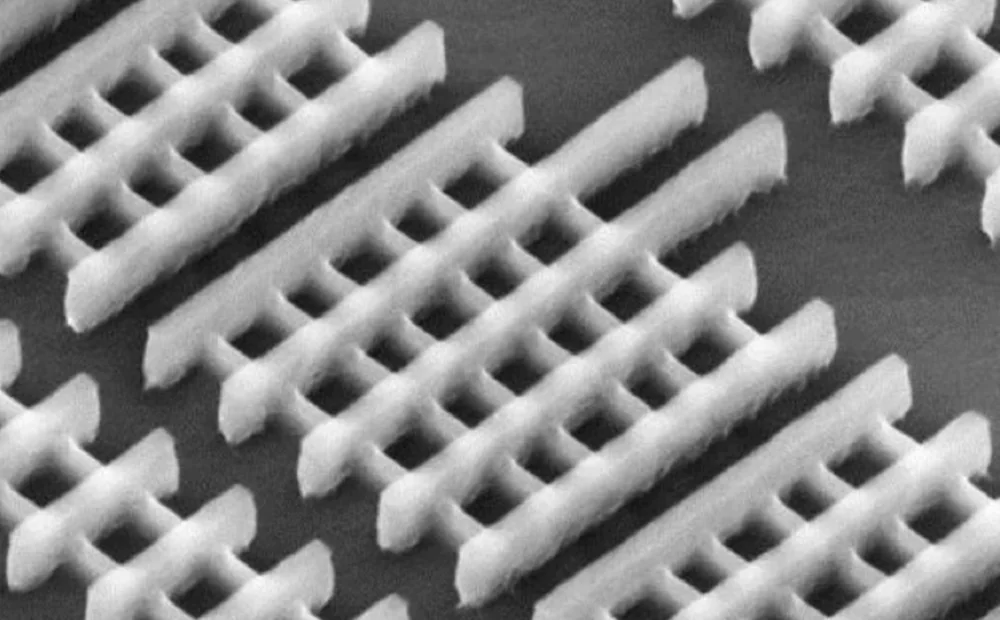

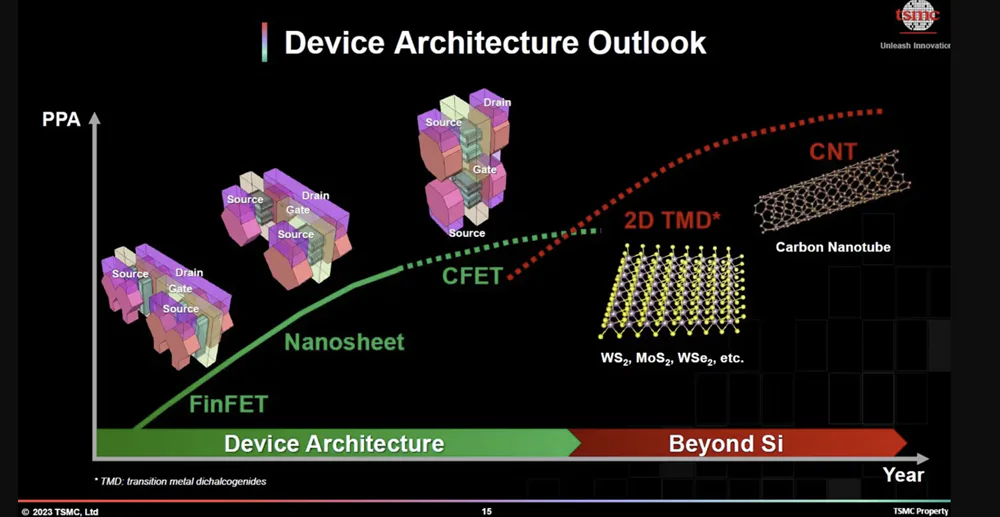

Зараз ми починаємо переходити в зону невизначеного майбутнього, дослідницьких робіт і загальних припущень, а не конкретних планів. Проте, спільнота цілком одностайна в тому, що настане час, коли транзистори потрібно буде розташувати один над одним, оскільки масштабування по осях Х і Y практично досягає межі. В даний час транзистори типу P і типу N розміщуються поруч один з одним. Мета полягає в тому, щоб укласти транзистори типу N на транзистори типу P, і таким чином створити “сендвічі” транзисторів, які називаються CFET (комплементарні FET). Досліджуються два основних способи досягнення такої конструкції: монолітний, при якому вся структура побудована на одній пластині, і послідовний, при якому транзистори N- і P-типу виготовляються на окремих пластинах, які “склеюються” разом.

За оцінками експертів, ринок виробництва мікропроцесорів увійде в третій вимір приблизно у 2032-2034 роках. Наразі відомо, що Intel і TSMC інтенсивно працюють над своїми реалізаціями цієї технології, але Samsung, ймовірно, теж не дрімає, адже потенційні переваги від використання цього рішення гігантські.

Також цікаво: Всесвіт: Найнезвичайніші космічні об’єкти

Перехід до “двох вимірів”

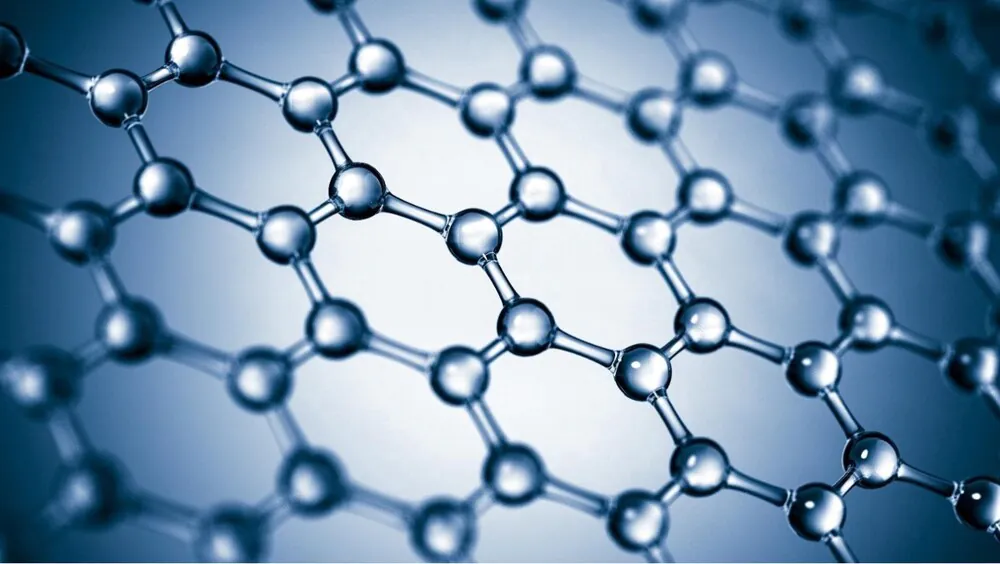

Ще одна проблема, з якою намагаються впоратися лідери світу виробництва мікросхем, полягає в тому, що банально не вистачає кремнію. Цей елемент служив нам вірою і правдою кілька десятиліть, але його обмежена кількість починає унеможливлювати подальше виготовлення все менших та швидших транзисторів. Тому в усьому світі тривають дослідження, так званих, двовимірних матеріалів, які могли б замінити кремній у каналі транзистора. Це матеріали, товщина яких може становити кілька, або лише один атом, і забезпечує рухливість електричного заряду, яка недоступна для кремнієвих напівпровідників такої товщини.

Найвідомішим двовимірним матеріалом є графен. Хоча можливості його використання у виробництві чипів все ще досліджуються, через відсутність природного енергетичного розриву є сумніви, чи він коли-небудь буде використаний у промислових масштабах для виробництво напівпровідників. Однак дослідження з використання сполук TMD (Transition Metal Dichalcogenides – сполуки перехідних металів d блоку періодичної таблиці та халькогенів 16-ї групи періодичної таблиці), таких як MoS 2 і WSe 2, що проводяться Intel і TSMC, виглядають досить перспективними. Ми зможемо побачити їх наслідки в наступному десятилітті.

Читайте також:

- Графенові мікрочипи зможуть зробити телефони швидше і легше

- Про квантові комп’ютери простими словами

Попереду цікаві часи

Підбиваючи підсумок, зауважу, що наступні роки будуть вщерть наповнені інноваціями та революціями у сфері виробництва напівпровідників. Вищеописані новації навіть не вичерпують тему, адже ми нічого не згадували ні про комп’ютерну літографію, ні про розробку чиплетів, ні про потенційний перехід на базу процесорів Glass. Ми також не говорили про прогрес у виробництві пам’яті.

Всім відомо, що такі переломні моменти ідеально підходять для надолуження технологічного відставання, оскільки велика ймовірність провалу у конкурентів. Intel навіть поставила все майбутнє компанії на те, що вона зможе запропонувати наступні напівпровідникові інновації швидше, ніж конкуренти. Уряд США також дуже зацікавлений у поверненні виробництва найсучасніших мікросхем до Північної Америки, тому він вкладає мільярди доларів у розробки компанії Intel. Однак субсидії на чипи – це не тільки сфера інтересів американців. У Кореї та на Тайвані уряди також надають щедрі преференції Samsung і TSMC, оскільки знають, наскільки важливий майбутній період і наскільки майбутнє цих країн залежить від нових технологій. Серед іншого, тому, що у них за плечима Китай, який теж вкладає величезні кошти у дослідження, розробку та розвиток виробництва напівпровідників, але це вже тема для іншої статті.

Читайте також:

- Ми всі станемо голограмами? Розвиток голографії від теорії до практики

- Спостереження за Червоною планетою: Історія марсіанських ілюзій